Loading…

Gemroc

Micromegas and GEMs semi-digital read-out chip

Description

GEMROC1 IS DEPRECATED – NOT RECOMMENDED FOR NEW DESIGN

Please consider Psiroc for new design

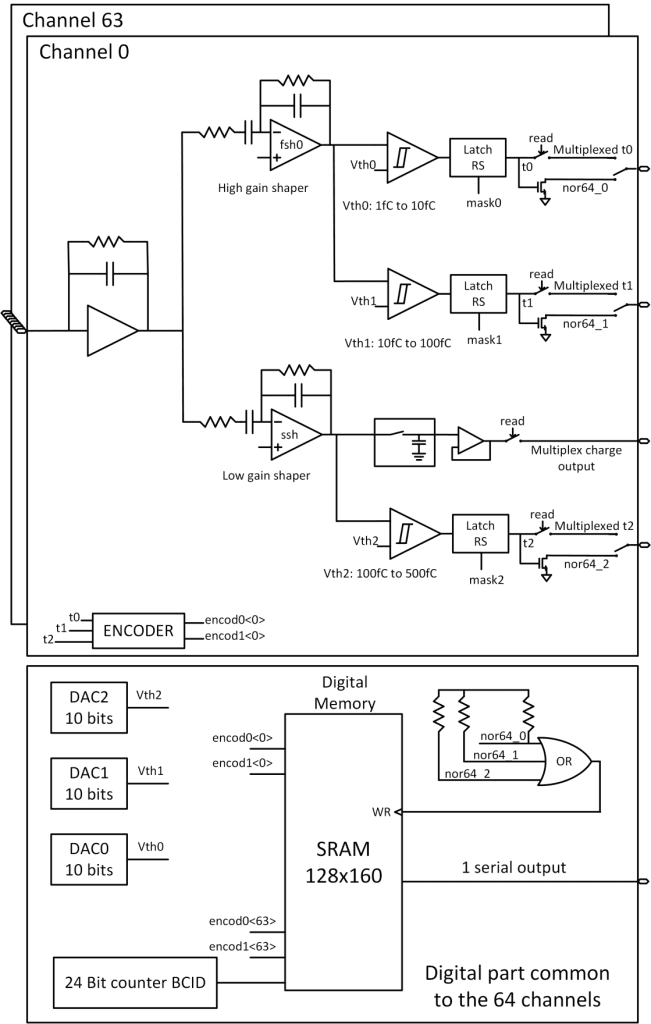

GEMROC 1 is a 64-channel front-end ASIC designed to readout negative fast (<1ns) and short (<10ns) current pulses from low gain detectors (GEMs, Micromegas, …). GEMROC 1 provides a semi-digital readout with three thresholds tunable from 1 fC to 500 fC and integrates a 128-deep digital memory to store the 2 x 64 discriminator outputs as well as the timestamp from a 24b counter. The three thresholds are set internally by three 10-bit DACs. The gain of each channel can be tuned individually from 0 to 2 over 8 bits, allowing the compensation of non-uniformity between the 64 detector channels. Each channel can auto trigger down to 1 fC input charge. A multiplexed charge measurement up to 500fC is integrated.

The power consumption is 1.5 mW/channel and the chip can be fully power-pulsed allowing a significant power reduction by disabling unused blocks.

Parameters

| Parameters | Value |

|---|---|

| TRLTechnology Readiness Level | 9 - Full system running ASIC , reliability proven |

| Available versions | 1 : DEPRECATED - please consider Psiroc |

| Detector Read-Out | GEMs, Micromegas |

| Number of Channel | 64 |

| Signal Polarity | Negative |

| Sensitivity | Trigger on 1 fC with 100% efficiency |

| Timing Resolution | Not relevant |

| Dynamic Range | 500fC |

| Packaging & Dimension | PQFP160 |

| Power Consumption | 100mW |

| Inputs | 64 current inputs |

| Outputs |

|

| Internal Programmable Features | Trigger threshold adjustment (10bits), |

| Evaluation systems | Evaluation system |

Diagram

Downloads

Downloads

Loading…

DISTRIBUTION NETWORK

All weeroc products are distributed worldwide by CAEN.

Please contact your local representative or get in touch with us.

Design review

Weeroc provide free support to review your board design integrating one of our ASIC. Get in touch with our engineering team to ensure a first-time-good design of your front-end electronics.